개요

고기능, 고집적, 저비용, 짧은 납기라는 고객의 요구를 바탕으로 광범위한 분야에서 FPGA 부품이 사용되고 있습니다. 상세 회로 설계 분야에서 High-Speed 대응이나 PCB상의 배선 효율 향상 등을 위하여 회로 설계, PCB 설계, 그리고 FPGA 설계의 각 설계 프로세스 간의 필연적인 결합이 이루어지고 있습니다.

예를 들어 PCB Layout/Layer 수의 제약에 따라 FPGA 부품에 접속하는 Differential Pair 신호 Line이나 Bus Line 등을 어느 Pin에 연결할지에 대한 검토와 반영이 이루어집니다. 그 높은 빈도와 정보량은 각 설계 프로세스에 소요되는 시간을 늘려 Human Error를 야기하기도 합니다.

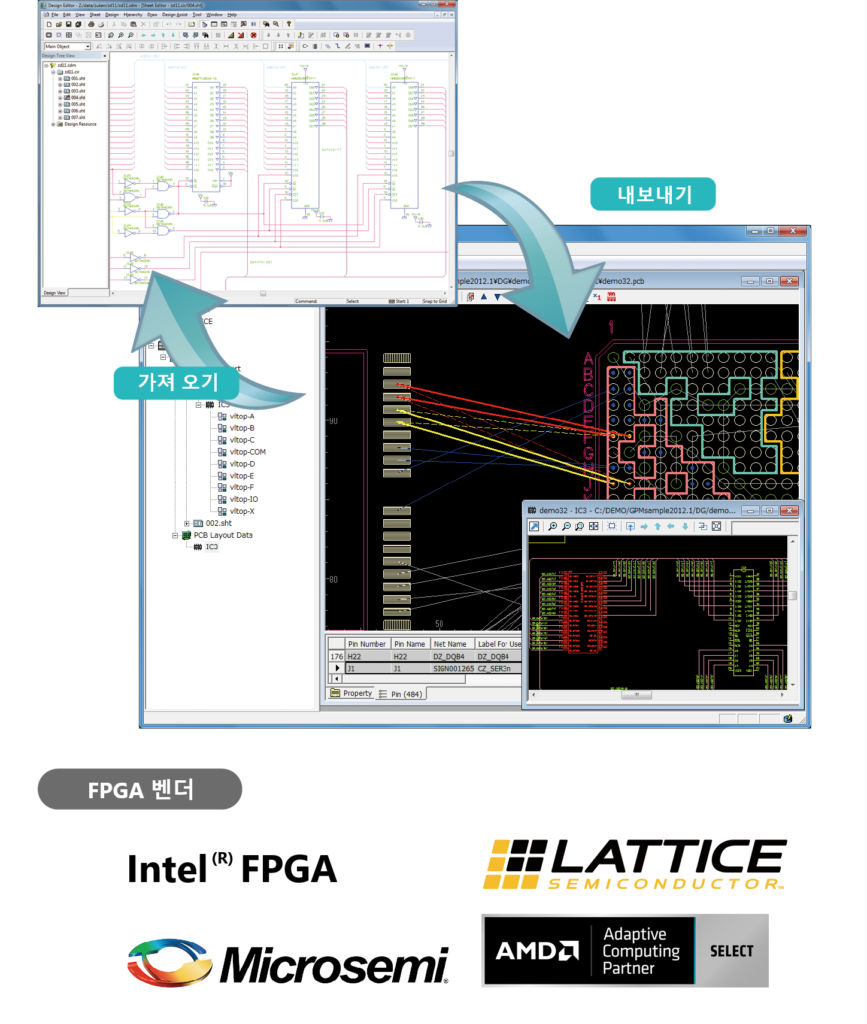

GPM은 각 설계 프로세스에 더해 CAD Library 관리 등의 연계를 통해 FPGA 부품을 둘러싼 회로/PCB 설계의 전체 최적화를 제공합니다.

- CAD Library, FPGA, 회로, PCB의 4가지 프로세스 연계

- PCB 전체의 FPGA 부품 설계 최적화

- Graphic View에 의한 정보 시각화

- 직감적인 툴 조작 환경 제공