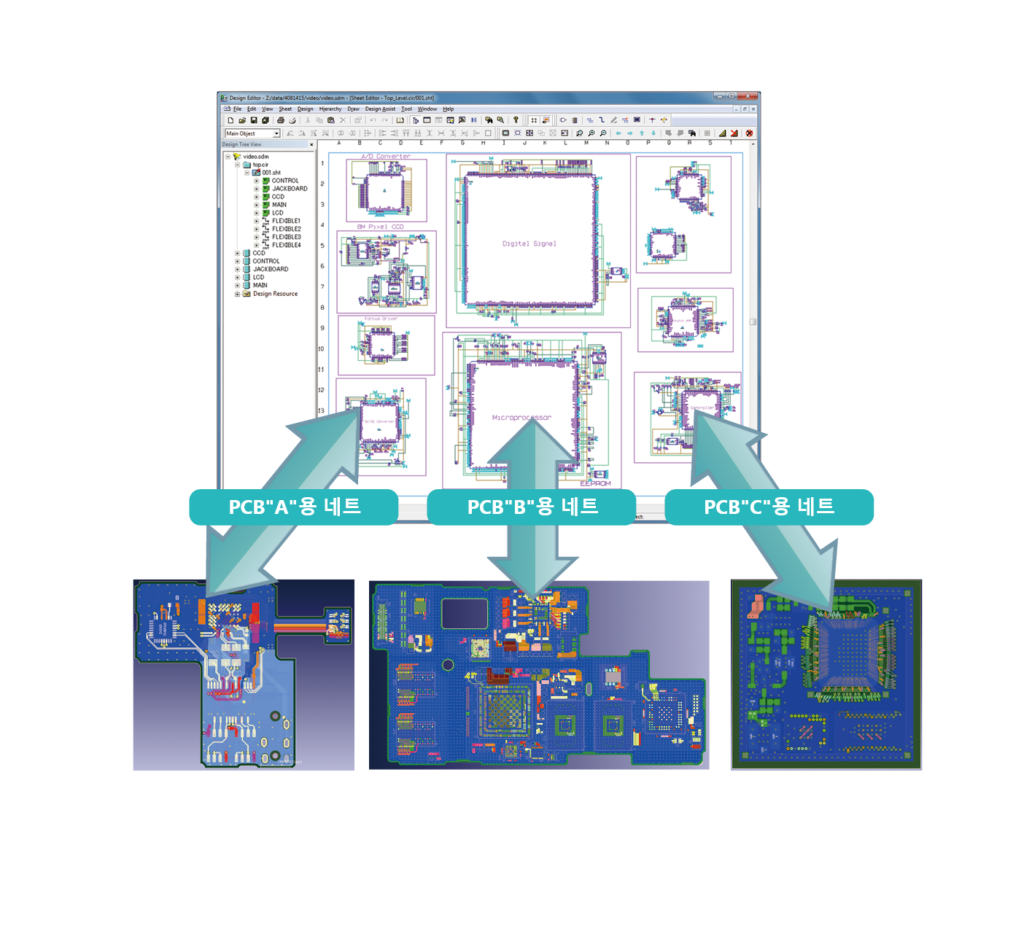

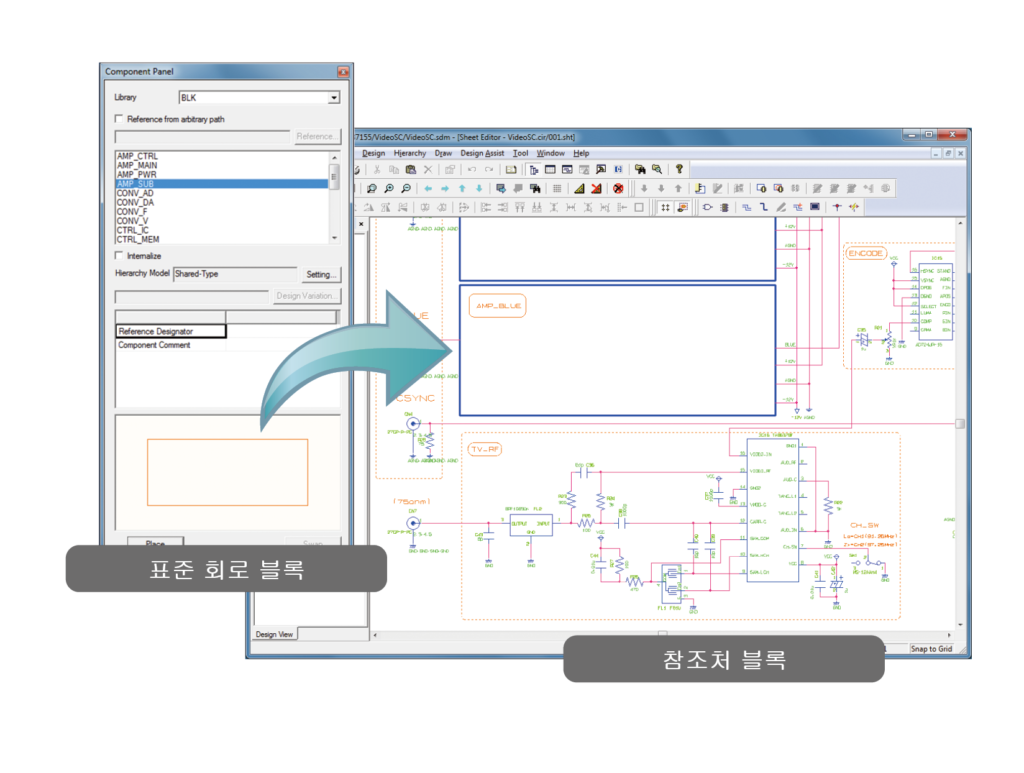

Hierarchy/회로블록을 사용한 Module 설계

Design Gateway는 표준화 시킬 기능블록이나 Module을 표준 회로블록으로 Library화할 수 있고, 표준회로블록은 회로에서 부품 Library와 같이 검색하거나 입력할 수 있습니다.

또 회로블록은 회로도에서 다양한 편집 권한 설정이 가능하며, 운용에 맞는 회로블록을 이용한 유용 설계를 할 수 있습니다.

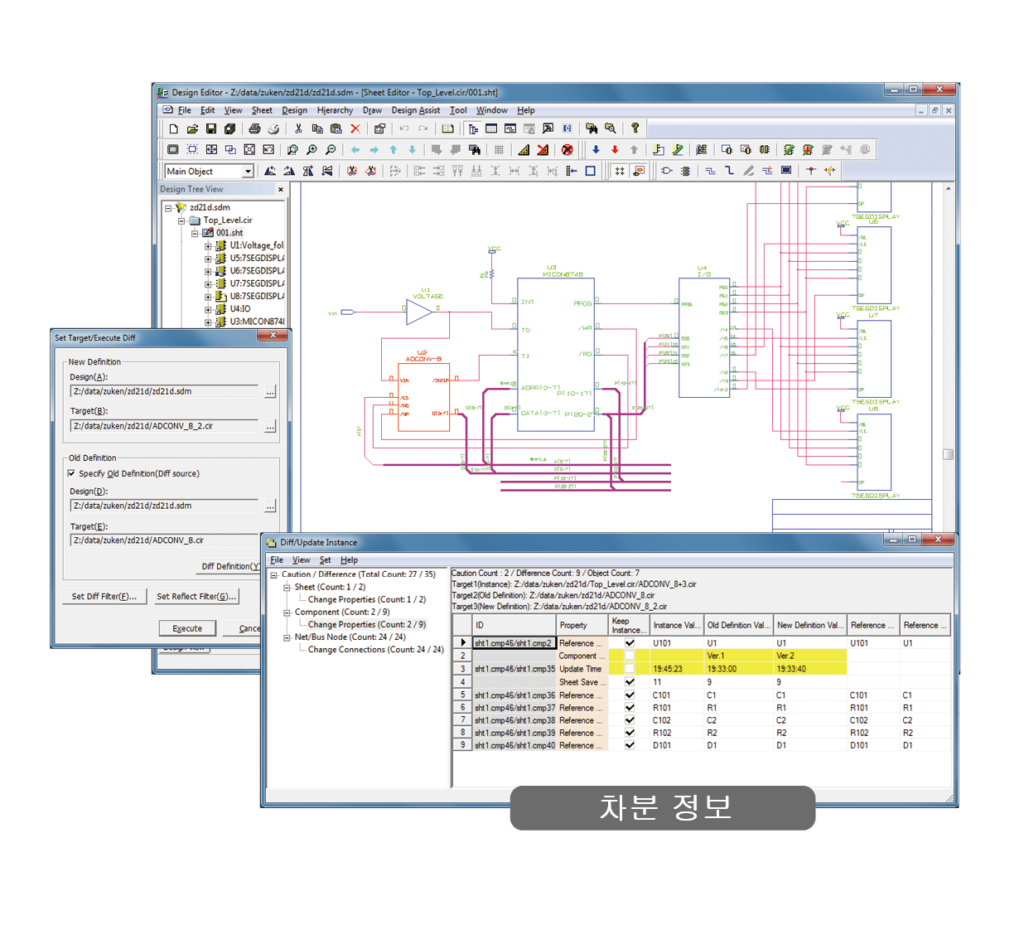

표준회로블록의 회로가 수정된 경우, 회로도에 사용된 회로블록과의 차분을 부품이나 Net 등의 Object별로 추출할 수 있습니다.

또 표준회로블록 정보를 회로도에서 사용 중인 회로블록에 반영할 때, 차분 별 회로블록의 정보를 유지시킬 수 있기 때문에 사용중인 회로블록의 수정 내용을 우선적으로 사용하고 싶은 경우에도 대응할 수 있습니다.